EMC Concept (2)

EMC Concept (2)

From EMC concept (1) , now we go forward to consider the rising and falling time.

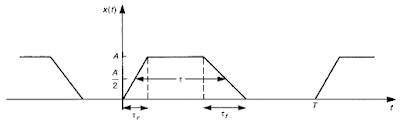

The condition is 50% duty cycle and we suppose the rising time is equal to falling time. After calculating, Cn and Co are shown below:

Consider the equation and the plot:

Consider the equation and the plot:

We match the above result to Cn:

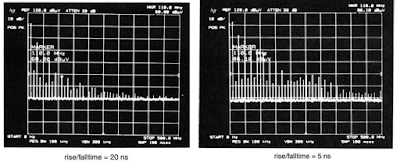

Suppose rising/falling times are 20ns and 5ns, we obtained the spectrum shown below. The 5ns pattern is worse than 20ns.

So the conclusions are:

1. Because τ = T / 2 = 1 / 2f, the higher frequency, the higher 1 / πτ. The -20 dB/decade will happen slowly.

2. The faster is the rising/falling time, the slower is the -20 dB/decade will occur.

This is why some designers who will reserved the capacitor on the clock signal. Slow down the rising/falling times and keep EMI becoming better. Remind that the value of capacitor cannot be too large, it may cause the system crashes.

Suppose rising/falling times are 20ns and 5ns, we obtained the spectrum shown below. The 5ns pattern is worse than 20ns.

So the conclusions are:

1. Because τ = T / 2 = 1 / 2f, the higher frequency, the higher 1 / πτ. The -20 dB/decade will happen slowly.

2. The faster is the rising/falling time, the slower is the -20 dB/decade will occur.

This is why some designers who will reserved the capacitor on the clock signal. Slow down the rising/falling times and keep EMI becoming better. Remind that the value of capacitor cannot be too large, it may cause the system crashes.

留言

張貼留言